RAMの簡単な説明。 RAM はどのような機能を果たしますか?

全文検索:

ホーム > 抄録 > 情報学

連邦教育庁

州立教育機関

高等専門教育

「サンクトペテルブルク州」

工経大学」

抽象的な

「PC RAM、種類、用途、主な特徴」

「情報学」という学問分野で

ヘッド A.A. カンタロヴィッチ

出演者 V. カルミコフ

グループ2601

サンクトペテルブルク

2010

1.RAM。 2

2.種類 ラム、その目的と主な特徴。 5

2.1 静的メモリ 5

3. スタティックメモリマトリクスの設計 6

4. スタティックメモリの種類 8

4.2 動的メモリ。 9

5. 動的メモリを操作するための手順と関数。 16

参考文献 21

1.RAM。

ランダム アクセス メモリは、国内の科学用語では「ランダム アクセス メモリ」または RAM、西洋の用語では RAM、つまり「ランダム アクセス メモリ」です。 RAM は、ソフトウェアが機能できるようにする一時的な記憶領域です。 メモリはセルで構成されており、各セルは一定量のデータ (通常は 1 ビットまたは 4 ビット) を格納するように設計されています。 メモリ チップはシステム バスと同期して動作します。 コンピュータの RAM はダイナミックです (したがって、DRAM またはダイナミック RAM)。このようなメモリにデータを保存するには、電流を一定に供給する必要があり、電流が供給されない場合、セルは空になります。 不揮発性メモリまたは読み取り専用メモリ (ROM または ROM - 読み取り専用メモリ) メモリの例はフラッシュ メモリです。フラッシュ メモリでは、電気は書き込みと読み取りにのみ使用され、データの保存自体には電源が必要ありません。 マイクロ回路内のメモリ セルは、論理 1 を書き込む必要がある場合に充電され、0 を書き込む場合に放電されるコンデンサです。 電力不足の場合のメモリの空化は、コンデンサからの漏れ電流によって正確に実行されます。

RAM の動作原理は次のように表すことができます。 セルは 2 次元マトリックスで構成されているため、特定のセルにアクセスするには、対応する行と列のアドレスを指定する必要があります。 アドレスの選択には、信号レベル(正確には電圧)がHighからLowに変化するRAS#(Row Access Strobe)パルスとCAS#(Column Acess Strobe)パルスが使用されます。 これらのパルスはクロック パルスと同期しているため、ランダム アクセス メモリは同期メモリ (SDRAM) とも呼ばれます。 まず、必要な回線のアクティブ化信号が送信され、続いて RAS# パルス、次に CAS# パルスが送信されます。 書き込み動作中も同じことが起こりますが、この場合は特別な書き込みイネーブル パルス WE# (書き込みイネーブル) が適用され、これもハイからローに変化する必要があります。 アクティブな行のすべてのセルでの作業が終了すると、プリチャージ コマンドが実行され、次の行に移動できるようになります。 他にも信号はありますが、内容が不必要に複雑になることを避けるため、この記事の文脈では言及できません。

パフォーマンスが依存するメモリの最も重要な特性は帯域幅です。帯域幅は、システム バス周波数とクロック サイクルごとに転送されるデータ量の積として表されます。 SDRAM メモリの場合、バス幅は 64 ビットまたは 8 バイトです。 したがって、たとえば、DDR333 メモリの帯域幅は 333 MHz x 8 バイト = 2.7 GB/秒、つまり 2700 MB/秒になります。 したがって、ちなみに、メモリの別の名前は、メガバイト/秒のスループットに基づいてPC2700です。 で 最近デュアル チャネル メモリ接続がよく使用され、理論上の帯域幅が 2 倍になります。 つまり、2 つの DDR333 モジュールの場合、最大 5.4 GB/s のデータ転送速度が得られます。

ただし、メモリ動作の周波数、つまり理論上の帯域幅だけがパフォーマンスに影響を与えるパラメータではありません。 実際には、メモリ レイテンシ、つまりコマンドの発行とその実行の間の遅延の値も同様に重要な役割を果たします。 これらの値は通常タイミングと呼ばれ、コマンドの受信から実際の実行までに経過したサイクルで表されます。特定のメモリ モジュールを説明するときに常に使用される 4 つの最も重要なタイミングは、tRCD、tCL、tRP、tRAS (コマンドレートが追加で示されることもあります)、通常は 4-4-4-12-(1T) の形式で同じ順序で書かれます (数字は この場合任意)。 略語 tRCD は、RAS# から CAS# までの遅延時間 (RAS# と CAS# パルスの間の遅延のタイミング) を表します。 略語 tCL は、CAS# レイテンシの時間を意味します。つまり、書き込みまたは読み取りコマンドの発行後の CAS# パルスに対する遅延のタイミングです。 tRP はロウプリチャージの時間です。ロウ処理が完了してからロウプリチャージに移行するまでのタイミングです。 改行。 tRAS (アクティブからプリチャージまでの遅延時間) 値は、ラインをアクティブにしてから、このラインの作業を終了するプリチャージ コマンドの発行までの遅延時間を表すため、主要パラメータの 1 つとみなされます。 最後に、コマンド レート パラメータは、モジュール上の特定のチップを選択するコマンドとラインをアクティブにするコマンドの間の遅延を意味します。 通常、この遅延は 1 クロック サイクルまたは 2 クロック サイクルを超えません。

一般的なルールは次のとおりです。1 つのタイミングが短ければ短いほど、 クロック周波数、メモリの速度が速くなります。 さらに、多くの場合、より低いクロック周波数でも動作する、より低いタイミングのメモリの方が高速であることが判明します。 問題は、すでに述べたように、RAM はシステム バスと同期して動作するため、システム バス周波数の倍数ではない周波数とシステム バス帯域幅を超える帯域幅を持つメモリには、安価なメモリと比べて何の利点もありません。 。 たとえば、最新の Pentium 4 プロセッサのシステム バスは 800 MHz の周波数で動作し、64 ビットのバス幅で 1 秒あたり 6.4 GB の最大スループットを提供します。 このようなチップに最適な選択肢は、同じ 6.4 GB/秒の同様の帯域幅を備えたデュアルチャネル DDR2 400 メモリです。 用途 2チャンネルモード DDR2 533/677 などのより高価なモジュールでは、パフォーマンスが実際に向上する可能性はほとんどありません。 さらに、他の場合には、そのようなモジュールの動作周波数を下げることが合理的ですが、より低いタイミングを実現します。 これはパフォーマンスにプラスの効果をもたらします。これを確認するには、さまざまなテスト プログラムを「実行」するだけです。

2. RAMの種類、その目的と主な特徴。

RAM にはさまざまな種類がありますが、それらはすべて、スタティック メモリ (スタティック RAM) とダイナミック メモリ (ダイナミック RAM) の 2 つの主要なサブグループに分類できます。

これら 2 種類のメモリの違いは、まず第一に、根本的に異なる技術実装です。SRAM は、新しいデータが書き込まれるか電源がオフになるまで記録されたデータを保存しますが、DRAM は短時間しかデータを保存できません。復元 (再生成) する必要があります。そうしないと、それらは失われます。

SRAM と DRAM の長所と短所を見てみましょう。

DRAM メモリは、そのテクノロジーにより、SRAM よりも高いデータ密度を持っています。

DRAM は SRAM よりもはるかに安価ですが、後者は常に読み取り可能な状態にあるため、生産性と信頼性が高くなります。

2.1 静的メモリ

スタティック メモリ、または SRAM (Statistic RAM) は、最も強力なタイプのメモリです。 SRAM チップは、ダイナミック メモリ チップを使用する RAM のキャッシュや、機械的記憶装置、ビデオ アダプタのメモリ ユニットなどのデータのキャッシュに使用されます。実際、SRAM チップは、必要なメモリ量がそれほど多くない場所で使用されます。大規模ですが、パフォーマンス要件は高く、そうであれば、高価なマイクロ回路の使用は正当化されます。 で パーソナルコンピュータオンチップ L2 キャッシュを持たないプロセッサでは、常に SRAM チップが使用されていました 外部キャッシュ。 マザーボードのコストとアップグレードの可能性を削減するために、プロセッサ 486 および第 1 世代の Pentium を搭載したマザーボードのメーカーは、さまざまな SRAM チップをインストールできる特別なベッド (DIP パッケージを備えたチップ用のソケット) を設置しました。速度とメモリ容量の両方、そしてビット深度が異なります。 メモリを構成するために、マザーボードにはジャンパのセットが用意されていました。 参考までに、ジャンパの取り付けに関する情報は、表に示すように、システム ボードに直接描かれています (列 JS1 および JS2 は、ジャンパで接続する必要がある接点の数を示します)。

マザーボード上のキャッシュ構成テーブルの例:

キャッシュ メモリ構成は、キャッシュ メモリ チップに障害が発生した場合にのみ変更されることに注意してください。 他の場合には、ジャンパーの位置を変更することは推奨されません。 その後、より高度な SRAM チップが開発されると、それらは 1 個、2 個、または 4 個の量でマザーボードに直接はんだ付けされるようになりました。 の上 マザーボード現在入手可能な SRAM チップは、主に I/O キャッシュおよびその他のシステム機能にのみ使用されます。

3. スタティックメモリマトリクスの設計

動的セルと同様に、トリガーは行と列で構成される 1 つの行列に結合され、後者はビットとも呼ばれます。

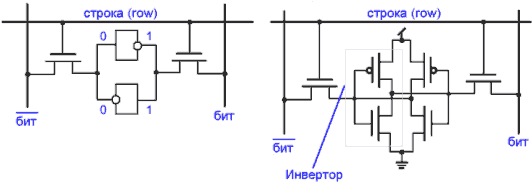

制御に必要なキートランジスタは 1 つだけであるダイナミック メモリ セルとは異なり、スタティック メモリ セルは少なくとも 2 つによって制御されます。 コンデンサとは異なり、トリガーには論理 0 と論理 1 をそれぞれ記録するための個別の入力があることを覚えていれば、これは驚くべきことではないでしょう。 したがって、スタティック メモリ セルごとに 8 個ものトランジスタが消費されます (図 2 を参照)。実際には、4 個がトリガー自体に使用され、さらに 2 個が制御「ラッチ」に使用されます。

米。 2. 6トランジスタシングルポートSRAMメモリセルの設計

さらに、セルごとに 6 個のトランジスタという制限はありません。 もっと複雑なデザインもありますよ! 6 トランジスタ セルの主な欠点は、一度にメモリ マトリックスの 1 行しか処理できないことです。 あるセルを読み出しながら別のセルを書き込むことは不可能であるのと同様に、同じバンクの異なる行にあるセルを並行して読み出すことは不可能です。

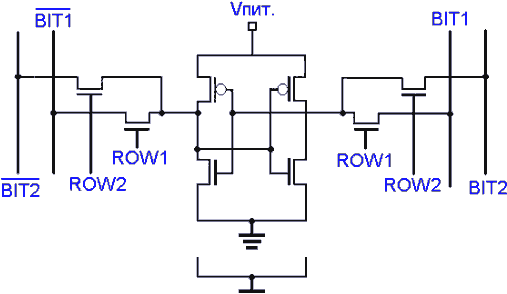

マルチポート メモリにはこの制限はありません。 各マルチポート メモリ セルには 1 つのフリップフロップが含まれていますが、複数の制御トランジスタ セットがあり、それぞれが独自の ROW ラインと BIT ラインに接続されているため、異なるマトリックス セルを独立して処理できます。 このアプローチは、メモリをバンクに分割するよりもはるかに進歩的です。 実際、後者の場合、並列処理は異なるバンクのセルにアクセスする場合にのみ実現されますが、これは常に実現可能であるわけではありません。また、マルチポート メモリにより任意のセルの同時処理が可能になり、プログラマはそのアーキテクチャの機能を詳しく調べる必要がなくなります。 。

最も一般的なのは 2 ポート メモリで、そのセル構造を図に示します。 3. (注意! これは、特に Intel Pentium マイクロプロセッサの 1 次キャッシュで使用されるメモリと同じではありません)。 2 ポート メモリの 1 つのセルを作成するには、8 つのトランジスタが消費されることを計算するのは簡単です。 キャッシュ メモリの容量を 32 KB とすると、コアが 1 つだけでも 200 万個以上のトランジスタが必要になります。

米。 3. 8 トランジスタ 2 ポート SRAM メモリ セルの設計

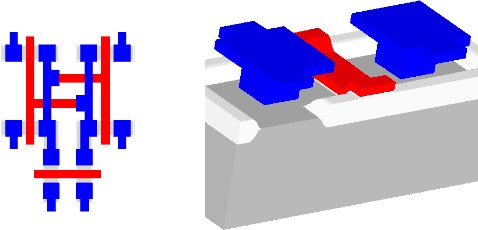

米。 3. 結晶内に組み込まれたダイナミックメモリセル

連邦教育庁

州立教育機関

高等専門教育

「サンクトペテルブルク州」

工経大学」

抽象的な

「PC RAM、種類、用途、主な特徴」

「情報学」という学問分野で

ヘッド A.A. カンタロヴィッチ

出演者 V. カルミコフ

グループ2601

サンクトペテルブルク

2010

コンテンツ。

1.RAM。 3

2. RAMの種類、その目的と主な特徴。 5

2.1 静的メモリ 6

3. スタティックメモリマトリクスの設計 7

4. 静的メモリの種類 8

4.2 動的メモリ。 9

5. 動的メモリを操作するための手順と関数。 17

参考文献 21

1.RAM.

ランダム アクセス メモリは、国内の科学用語では「ランダム アクセス メモリ」または RAM、西洋の用語では RAM、つまり「ランダム アクセス メモリ」です。 RAM は、ソフトウェアが機能できるようにする一時的な記憶領域です。 メモリはセルで構成されており、各セルは一定量のデータ (通常は 1 ビットまたは 4 ビット) を格納するように設計されています。 メモリ チップはシステム バスと同期して動作します。 コンピュータの RAM はダイナミックです (したがって、DRAM またはダイナミック RAM)。このようなメモリにデータを保存するには、電流を一定に供給する必要があり、電流が供給されない場合、セルは空になります。 不揮発性メモリまたは読み取り専用メモリ (ROM または ROM - 読み取り専用メモリ) メモリの例はフラッシュ メモリです。フラッシュ メモリでは、電気は書き込みと読み取りにのみ使用され、データの保存自体には電源が必要ありません。 マイクロ回路内のメモリ セルは、論理 1 を書き込む必要がある場合に充電され、0 を書き込む場合に放電されるコンデンサです。 電力不足の場合のメモリの空化は、コンデンサからの漏れ電流によって正確に実行されます。 (図1)図1

RAM の動作原理は次のように表すことができます。 セルは 2 次元マトリックスで構成されているため、特定のセルにアクセスするには、対応する行と列のアドレスを指定する必要があります。 アドレスの選択には、信号レベル(正確には電圧)がHighからLowに変化するRAS#(Row Access Strobe)パルスとCAS#(Column Acess Strobe)パルスが使用されます。 これらのパルスはクロック パルスと同期しているため、ランダム アクセス メモリは同期メモリ (SDRAM) とも呼ばれます。 まず、必要な回線のアクティブ化信号が送信され、続いて RAS# パルス、次に CAS# パルスが送信されます。 書き込み動作中も同じことが起こりますが、この場合は特別な書き込みイネーブル パルス WE# (書き込みイネーブル) が適用され、これもハイからローに変化する必要があります。 アクティブな行のすべてのセルでの作業が終了すると、プリチャージ コマンドが実行され、次の行に移動できるようになります。 他にも信号はありますが、内容が不必要に複雑になることを避けるため、この記事の文脈では言及できません。

パフォーマンスが依存するメモリの最も重要な特性は帯域幅です。帯域幅は、システム バス周波数とクロック サイクルごとに転送されるデータ量の積として表されます。 SDRAM メモリの場合、バス幅は 64 ビットまたは 8 バイトです。 したがって、たとえば、DDR333 メモリの帯域幅は 333 MHz x 8 バイト = 2.7 GB/秒、つまり 2700 MB/秒になります。 したがって、ちなみに、メモリの別名は、メガバイト/秒のスループットに基づいてPC2700です。 最近では、理論上の帯域幅が 2 倍になるデュアル チャネル メモリ接続がよく使用されます。 つまり、2 つの DDR333 モジュールの場合、最大 5.4 GB/s のデータ転送速度が得られます。

ただし、メモリ周波数、つまり理論上の帯域幅だけがパフォーマンスに影響を与えるパラメータではありません。 実際には、メモリ レイテンシ、つまりコマンドの発行と実行の間の遅延も同様に重要な役割を果たします。 これらの値は通常タイミングと呼ばれ、コマンドの受信から実際の実行までに経過したサイクルで表されます。特定のメモリ モジュールを説明するときに常に使用される 4 つの最も重要なタイミングは、tRCD、tCL、tRP、tRAS (コマンド レートを追加で示すこともあります)、通常は 4-4-4-12-(1T) の形式で同じ順序で記述されます (この場合の数字は任意です)。 略語 tRCD は、RAS# から CAS# までの遅延時間 (RAS# と CAS# パルスの間の遅延のタイミング) を表します。 略語 tCL は、CAS# レイテンシの時間を意味します。つまり、書き込みまたは読み取りコマンドの発行後の CAS# パルスに対する遅延のタイミングです。 tRP は行プリチャージの時間、つまり行処理の完了と新しい行への移行の間のタイミングです。 tRAS (アクティブからプリチャージまでの遅延時間) 値は、ラインをアクティブにしてから、このラインの作業を終了するプリチャージ コマンドの発行までの遅延時間を表すため、主要パラメータの 1 つとみなされます。 最後に、コマンド レート パラメータは、モジュール上の特定のチップを選択するコマンドとラインをアクティブにするコマンドの間の遅延を意味します。 通常、この遅延は 1 クロック サイクルまたは 2 クロック サイクルを超えません。

一般的なルールは、1 つのクロック周波数でのタイミングが低いほど、メモリが高速になるということです。 さらに、多くの場合、より低いクロック周波数でも動作する、より低いタイミングのメモリの方が高速であることが判明します。 問題は、すでに述べたように、RAM はシステム バスと同期して動作するため、システム バス周波数の倍数ではない周波数とシステム バス帯域幅を超える帯域幅を持つメモリには、安価なメモリと比べて何の利点もありません。 。 たとえば、最新の Pentium 4 プロセッサのシステム バスは 800 MHz の周波数で動作し、64 ビットのバス幅で 1 秒あたり 6.4 GB の最大スループットを提供します。 このようなチップに最適な選択肢は、同じ 6.4 GB/秒の同様の帯域幅を備えたデュアルチャネル DDR2 400 メモリです。 DDR2 533/677 などのより高価なモジュールをデュアルチャネル モードで使用しても、パフォーマンスが実際に向上する可能性はほとんどありません。 さらに、他の場合には、そのようなモジュールの動作周波数を下げることが合理的ですが、より低いタイミングを実現します。 これはパフォーマンスにプラスの効果をもたらします。これを確認するには、さまざまなテスト プログラムを「実行」するだけです。

2. RAMの種類、その目的と主な特徴。

RAM にはさまざまな種類がありますが、それらはすべて、スタティック メモリ (スタティック RAM) とダイナミック メモリ (ダイナミック RAM) の 2 つの主要なサブグループに分類できます。これら 2 種類のメモリの違いは、まず第一に、根本的に異なる技術実装です。SRAM は、新しいデータが書き込まれるか電源がオフになるまで記録されたデータを保存しますが、DRAM は短時間しかデータを保存できません。復元 (再生成) する必要があります。そうしないと、それらは失われます。

SRAM と DRAM の長所と短所を見てみましょう。

DRAM メモリは、そのテクノロジーにより、SRAM よりも高いデータ密度を持っています。

DRAM は SRAM よりもはるかに安価ですが、後者は常に読み取り可能な状態にあるため、生産性と信頼性が高くなります。

2.1 静的メモリ

スタティック メモリ、または SRAM (Statistic RAM) は、最も強力なタイプのメモリです。 SRAM チップは、ダイナミック メモリ チップを使用する RAM のキャッシュや、機械的記憶装置、ビデオ アダプタのメモリ ユニットなどのデータのキャッシュに使用されます。実際、SRAM チップは、必要なメモリ量がそれほど多くない場所で使用されます。大規模ですが、パフォーマンス要件は高く、そうであれば、高価なマイクロ回路の使用は正当化されます。 オンチップ L2 キャッシュを持たないプロセッサを搭載したパーソナル コンピュータは、常に外部キャッシュ SRAM チップを使用していました。 マザーボードのコストとアップグレードの可能性を削減するために、プロセッサ 486 および第 1 世代の Pentium を搭載したマザーボードのメーカーは、さまざまな SRAM チップをインストールできる特別なベッド (DIP パッケージを備えたチップ用のソケット) を設置しました。速度とメモリ容量の両方、そしてビット深度が異なります。 メモリを構成するために、マザーボードにはジャンパのセットが用意されていました。 参考までに、ジャンパの取り付けに関する情報は、表に示すように、システム ボードに直接描かれています (列 JS1 および JS2 は、ジャンパで接続する必要がある接点の数を示します)。マザーボード上のキャッシュ構成テーブルの例:

| サイズ | SRAM | JS1 | JS2 |

| 256K | 32x8 | 1-2 | 1-2 |

| 512K | 64x8 | 2-3 | 1-2 |

| 1メートル | 128x8 | 2-3 | 2-3 |

3. スタティックメモリマトリクスの設計

動的セルと同様に、トリガーは行と列で構成される 1 つの行列に結合され、後者はビットとも呼ばれます。制御に必要なキートランジスタは 1 つだけであるダイナミック メモリ セルとは異なり、スタティック メモリ セルは少なくとも 2 つによって制御されます。 コンデンサとは異なり、トリガーには論理 0 と論理 1 をそれぞれ記録するための個別の入力があることを覚えていれば、これは驚くべきことではないでしょう。 したがって、スタティック メモリ セルごとに 8 個ものトランジスタが消費されます (図 2 を参照)。実際には、4 個がトリガー自体に使用され、さらに 2 個が制御「ラッチ」に使用されます。

米。 2. 6トランジスタシングルポートSRAMメモリセルの設計

さらに、セルごとに 6 個のトランジスタという制限はありません。 もっと複雑なデザインもありますよ! 6 トランジスタ セルの主な欠点は、一度にメモリ マトリックスの 1 行しか処理できないことです。 あるセルを読み出しながら別のセルを書き込むことは不可能であるのと同様に、同じバンクの異なる行にあるセルを並行して読み出すことは不可能です。

マルチポート メモリにはこの制限はありません。 各マルチポート メモリ セルには 1 つのフリップフロップが含まれていますが、複数の制御トランジスタ セットがあり、それぞれが独自の ROW ラインと BIT ラインに接続されているため、異なるマトリックス セルを独立して処理できます。 このアプローチは、メモリをバンクに分割するよりもはるかに進歩的です。 実際、後者の場合、並列処理は異なるバンクのセルにアクセスする場合にのみ実現されますが、これは常に実現可能であるわけではありません。また、マルチポート メモリにより任意のセルの同時処理が可能になり、プログラマはそのアーキテクチャの機能を詳しく調べる必要がなくなります。 。

最も一般的なのは 2 ポート メモリで、そのセル構造を図に示します。 3. (注意! これは、特に Intel Pentium マイクロプロセッサの 1 次キャッシュで使用されるメモリと同じではありません)。 2 ポート メモリの 1 つのセルを作成するには、8 つのトランジスタが消費されることを計算するのは簡単です。 キャッシュ メモリの容量を 32 KB とすると、コアが 1 つだけでも 200 万個以上のトランジスタが必要になります。

米。 3. 8 トランジスタ 2 ポート SRAM メモリ セルの設計

米。 3. 結晶内に組み込まれたダイナミックメモリセル

4. 静的メモリの種類

静的メモリには、非同期、同期、パイプラインの少なくとも 3 つのタイプがあります。 それらはすべて、対応するタイプの動的メモリと実質的に変わりません。非同期スタティックメモリ

非同期スタティック メモリはコントローラとは独立して動作するため、コントローラは交換サイクルの終わりが次のクロック パルスの始まりと一致するかどうかを確認できません。 その結果、通信サイクルが少なくとも 1 クロック サイクル延長され、実効パフォーマンスが低下します。 後者の状況の「おかげで」、現在、非同期メモリは事実上どこでも使用されていません(非同期メモリが二次キャッシュとしてまだ使用されていた最後のコンピュータは「3 ルーブル」でした。これに基づいて構築されたマシンです) インテルプロセッサー 80386).

同期スタティックメモリ

同期スタティック メモリはすべての操作をクロック信号と同時に実行するため、単一セルのアクセス時間は 1 クロック サイクル内になります。 最新のプロセッサの 1 次キャッシュは同期スタティック メモリ上に実装されています。

パイプライン静的メモリ

パイプライン静的メモリは同期メモリです 静的メモリ、データラインを保持する特別な「ラッチ」を備えており、これにより、アドレスを別のセルに送信するのと並行して、あるセルの内容を読み取る(書き込む)ことができます。

また、パイプライン メモリは、1 つの作業サイクルで複数の隣接するセルを処理できます。 パケットの最初のセルのアドレスのみを送信するだけで十分で、マイクロ回路は残りのアドレスを独自に計算します。書き込み(読み取り)データを送信(受信)するだけの時間があります。

パイプライン メモリのハードウェアの複雑さにより、パケットの最初のセルへのアクセス時間は 1 クロック サイクル増加しますが、これによって実際にはパフォーマンスが低下することはありません。 パケット内の後続のすべてのセルは遅延なく処理されます。

パイプライン静的メモリは、特に Pentium-II マイクロプロセッサの 2 次キャッシュで使用され、その式は次のようになります: 2-1-1-1。

4.2 動的メモリ。

プログラム内で宣言されたすべての変数は、データ セグメントと呼ばれる RAM の 1 つの連続した領域に配置されます。 データ セグメントの長さは 8086 マイクロプロセッサのアーキテクチャによって決まり、65,536 バイトです。これにより、大量のデータを処理するときに既知の問題が発生する可能性があります。一方、PC メモリの量 (通常は少なくとも 640 KB) は、大きなデータ次元の問題を正常に解決するのに十分です。 解決策としては、いわゆる動的メモリを使用することが考えられます。

ダイナミック メモリは、プログラムの動作中にプログラムに提供される PC RAM から、F4 KB データ セグメントを差し引いたもの、スタック (通常は 16 KB)、およびプログラム本体自体です。

動的メモリのサイズは、広い制限内で変更できます (付録 1 を参照)。 デフォルトでは、このサイズは利用可能なすべての PC メモリによって決まり、原則として少なくとも 200 ~ 300 KB です。 実際、動的メモリは大規模なデータ配列を処理する唯一の方法です。 動的メモリがなければ、多くの実際的な問題を解決することは困難または不可能です。

このようなニーズは、たとえば、コンピュータ支援設計 (CAD) システムを開発するときに発生します。CAD で使用される数学的モデルの寸法は、プロジェクトによって大きく異なる場合があります。 この場合の静的 (つまり、CAD 開発段階での) メモリ割り当ては、原則として不可能です。 最後に、ダイナミック メモリは、PC グラフィックスおよびオーディオ ツールを使用する際のデータの一時保存に広く使用されています。

動的データ配置とは、プログラムの実行中に動的メモリを直接使用することを意味します。 対照的に、静的割り当ては、プログラムのコンパイル中に Turbo Pascal コンパイラーによって実行されます。 動的配置では、配置されるデータのタイプも量も事前にわかりません。静的変数のように、名前でアクセスすることはできません。

PC RAM は、情報 (バイト) を保存するための基本セルの集合であり、それぞれのセルには 自分の番号。 これらの番号はアドレスと呼ばれ、メモリの任意のバイトにアクセスできるようになります。

Turbo Pascal は、動的メモリ、いわゆるポインタを管理する柔軟な手段をプログラマに提供します。 ポインタは、メモリのバイトのアドレスを値として含む変数です。

PC では、アドレスはセグメントとオフセットと呼ばれる 2 つの 16 ビット ワードの組み合わせによって指定されます。 セグメントは 65,536 バイト (F4 KB) の長さのメモリで、16 の倍数 (0、16、32、48 など) の物理アドレスで始まります。 オフセットは、目的のアドレスに到達するためにセグメントの先頭から何バイトスキップする必要があるかを指定します。 PC のアドレス空間は 1 MB です (いわゆる標準的な PC メモリについて話しています。プロセッサ 80386 以降を搭載した最新のコンピュータでは、アドレス空間は 4 GB ですが、Turbo Pascal には追加メモリの使用をサポートするツールがありません。 Borland Pascal を Objects 環境 7.0 で使用する場合、このオプションが利用可能です)。

1 MB 以内のアドレスを指定するには、20 バイナリ ビットが必要です。これは、次のように 2 つの 16 ビット ワード (セグメントとオフセット) から取得されます (図 6.1)。セグメントの内容は 4 ビット左にシフトされ、空いたビットは 2 つの 16 ビット ワード (セグメントとオフセット) から取得されます。右側のビットがゼロで埋められると、その結果がオフセットの内容に追加されます。 16 バイトのメモリの塊は段落と呼ばれるため、セグメントは段落精度でメモリをアドレス指定し、バイト精度でオフセットをアドレス指定すると言えます。 各セグメントは、連続した個別にアドレス指定可能なメモリ領域に対応します。 セグメントは、メモリ内で隙間なく、または一定の間隔を置いて互いに続くことも、最終的には互いに重なり合うこともあります。 したがって、その内部構造では、すべてのポインターは 2 つの単語 (WORD データ) の集合であり、セグメント 154 として解釈されます。

ポインターを使用すると、Turbo Pascal で知られている任意のデータ型を動的メモリに配置できます。 それらの一部 (BYTE、CHAR、SHORTINT、BOOLEAN) だけが内部表現で 1 バイトを占め、残りはいくつかの隣接するバイトを占めます。 したがって、ポインタは実際にはデータの最初のバイトのみをアドレス指定します。 6.3. ポインタの宣言。

通常、Turbo Pascal では、ポインターは何らかのデータ型に関連付けられます。 このようなポインターを型付きと呼びます。 型付きポインターを宣言するには、対応する型の前に配置される l アイコンが使用されます。例: var pi AInteger; p2: "実数; タイプ PerconPomter = "PcrconRecord; PerconRecord = レコード名: 文字列; ジョブ: 文字列。 次へ: PerconPomter 終了。 注意: PerconPointer 型を宣言するとき、プログラム内で以前に宣言されていなかった PerconRecord 型を参照しました。 すでに述べたように、Turbo Pascal は、識別子を使用する前にそれを記述する必要があるという原則を一貫して適用します。 まだ宣言されていないデータ型を参照できるポインターについてのみ例外が発生します。 これは偶然に起こったことではありません。

動的メモリにより、一部のプログラムで広く使用されているリストの形式でデータを編成することが可能になります。 各リスト要素には隣接する要素へのポインタが含まれており (図 6.2)、これによりリストを表示および修正することができます。 Turbo Pascal にこの例外がなかったら、リストの実装は大幅に困難になっていたでしょう。 Turbo Pascal では、特定のデータ型に関連付けずにポインターを宣言できます。 これには標準タイプ POINTER が使用されます (例: var p: pointer)。

リストの最初の要素 インデックス - リストの 2 番目の要素 リストの最後の要素 NIL 図 6.2. リスト データ構造 この種のポインターをスパイクなしと呼びます。 型なしポインターは特定の型に関連付けられていないため、プログラムの実行中に構造と型が変化するデータを動的に割り当てるために使用できます。

すでに述べたように、ポインタの値はメモリ内の変数のアドレスであるため、あるポインタの値を別のポインタに渡すことができることが期待されます。 実際、これは完全に真実ではありません。 Turbo Pascal では、同じデータ型に関連付けられたポインター間でのみ値を渡すことができます。 たとえば、変数 pl,p2 の場合、 「整数; p3: lYaoa1; pp: ポインタ; この場合、代入 pl:= p2; は完全に正当ですが、代入 pl:= p3; は禁止されています。これは、P1 と p3 が pa を示しているためです。 さまざまな種類データ。 ただし、この制限は型なしポインターには適用されないため、 pp:- p3, pl:= pp; と書くことができます。 そしてそれによって望ましい結果が得られます。

読者には、制限を導入し、それを回避する手段を直ちに提供する価値があるかどうかを問う権利があります。 重要なのは、制限は、一方ではプログラムの信頼性を高めるために導入されるものですが、他方では言語の能力を低下させ、一部のアプリケーションには適さないものにしてしまうということです。

Turbo Pascal では、データ型のいくつかの例外により言語に必要な柔軟性が与えられますが、その使用にはプログラマ側で追加の努力が必要となるため、非常に意識的なアクションが必要になります。

動的メモリの割り当てと解放 Turbo Pascal のすべての動的メモリは、ヒープと呼ばれる連続したバイト配列として扱われます。 物理的には、ヒープはプログラム本体が占めるメモリ領域の直後の上位アドレスに位置します。 ヒープの先頭は標準の HeapOrg 変数 (図 6.3) に格納され、末尾は HeapEnd 変数に格納されます。 未割り当ての動的メモリの現在の制限は、Heapptr 変数に含まれています。 動的に割り当てられた変数のメモリは、NEW プロシージャによって割り当てられます。 このプロシージャを呼び出すためのパラメータは型付きポインタです。 アクセスの結果、ポインタは動的アドレスに対応する値を取得し、そこからデータを配置できます (例: var i, j: "Integer; r: AReal; begin New(i); end)。

このフラグメントの実行後、ポインタ 1 はヒープ ポインタ HEAPPTR が以前に持っていた値を取得し、ポインタ I が関連付けられている INTEGER 型の内部表現の長さが 2 であるため、HEAPPTR 自体はその値を 2 増やします。バイト (実際には、これは完全に真実ではありません。変数のメモリは 8 バイトの倍数の部分に割り当てられます。セクション 6.7 を参照)。 演算子 new(g); HEAPPTR ポインタが再びオフセットされますが、これは REAL 型の内部表現の長さであるため、他の型の変数にも同様にメモリが割り当てられます。 ポインタが特定の値を取得した後、つまり、メモリの特定の物理バイトを指し始めた後、対応するタイプの任意の値をこのアドレスに配置できます。 これを行うには、ポインタの直後にスペースを入れずにシンボル l を配置します。例: i = 2, (値 2 はメモリ領域 i に配置されます) i = 2*pi; (値 6.28 はメモリ領域 g に配置されます)\

PC メモリ内のヒープの位置 したがって、ポインタが指す値、つまりヒープ内にある実際のデータは、ポインタの直後に配置される L アイコンによって示されます。 ポインタの後ろにアイコンがない場合、これはデータが配置されているアドレスを意味します。 今述べたことをもう一度考えるのは理にかなっています。ポインターの値はアドレスであり、アドレスについて話しているのではなく、このアドレスにあるデータについて話していることを示すために、L がアドレスの後に置かれます。これを明確に理解していれば、動的メモリを扱うときに問題は発生しません。 動的に割り当てられたデータは、適切な型の定数および変数が許可されるプログラム内のどこでも使用できます。例: gL:<* sqr (rA) + \Л - 17; Разумеется, совершенно недопустим оператор г:= sqr(rA) + iA - 17; т. к. указателю r нельзя присвоить значение вещественного выражения. Точно так же недопустим оператор гл:= sqr (г) ; поскольку значением указателя r является адрес, и его (в отличие от того значения, которое размещено по этому адресу) нельзя возводить в квадрат. Ошибочным будет и такое присваивание: =х; 158 Ядро Турбо Паскаля т. к. вещественным данным, на которые указывает R, нельзя присвоить значение указателя (адрес).

動的メモリはヒープから取り出すだけでなく、戻すこともできます。 これを行うには、DISPOSE プロシージャを使用します。 たとえば、演算子は破棄されます) ; 処分(i); ポインタ 1 と R に以前に割り当てられていた 8 バイトをヒープに返します (上記を参照)。 dtspose (PTR) プロシージャは PTR ポインタの値を変更せず、このポインタに以前関連付けられていたメモリをヒープに返すだけであることに注意してください。 ただし、プロシージャを空きポインタに再適用すると、実行時エラーが発生します。 プログラマは、解放されたポインタに予約語 NIL をマークできます。 ポインタがマークされているかどうかは、次のようにして確認できます。 p = NIL の場合に開始し、その後 new(p); 破棄(p) ; p:なし。 終わり。 ポインターに対する他の比較演算は許可されません。 上記のスニペットは、ポインタを型付き定数として宣言し (第 7 章を参照)、同時に値 NIL を割り当てる好ましい方法を示しています。 ポインターの初期値 (変数セクションで宣言されている場合) は任意であることに注意してください。 NEW プロシージャなどによって値が割り当てられていないポインタの使用はシステムによって制御されず、予期しない結果が生じる可能性があります。

等.............

RAM はどのような機能を果たしますか?

マスターの答え:

RAM は、プロセッサが特定の操作を実行するために必要なデータとコマンドを一時的に保存する機能を実行します。 データは直接、または超高速メモリを介して RAM に入力されます。 すべての情報はコンピュータの電源を入れたときにのみ保存され、電源を切るとすべてのデータが消去されます。

プログラムが実行されると、その最も重要なファイルの一部がランダム アクセス メモリ (RAM) にロードされ、アプリケーションが終了するまで保持されます。 そして、プロセッサ自体がこれらのファイルを直接実行し、結果を保存します。 押されたキーのすべてのコードと実行された数学演算の値はメモリに保存されます。 「保存」コマンドを実行すると、RAM にあるすべての内容がハードドライブに保存されます。

ロードされるすべてのプロセスの速度は RAM に依存するため、ほとんどの PC ユーザーは RAM の量を増やそうと努めています。 これは、ゲームやさまざまなグラフィック エディタなど、リソースを大量に消費するプログラムを実行する場合に特に役立ちます。 したがって、RAM の量が多いほど、ゲームプレイと編集が高速になります。

RAMには多くの種類があります。 最も一般的なのは DDR、DDRII、DDRIII で、それぞれの違いはデータ転送の周波数にあります。 周波数が高いほど作業は速くなります。 これらの中で最も遅いのは DDR で、最も速いのは DDR3 です。 これらのストリップにはすべて異なるコネクタがあります。

各モジュールには、システムボードに接続するマイクロ回路が含まれています。 これらのモジュールには異なる特性があり、使用されるシステムと互換性がある必要があります。

ROM は読み取り専用のストレージデバイスであるため、ユーザーは書き込み操作を実行できません。 DRAM はダイナミック ランダム アクセス メモリ デバイスです。 SRAM はスタティック ランダム アクセス メモリです。 ROM と DRAM はデータ ストレージをサポートしていますが、変更することはできません。 このため、システム自体を起動するプログラムがロードされています。 ROM はシステムの RAM の一部と考えることができ、スティックの一部には重要なソフトウェアをロードするためのアドレス空間があります。

他のものとは別に、RAM は超小型回路です。 片面または両面にモジュールが配置された片面ストリップと両面ストリップがあります。